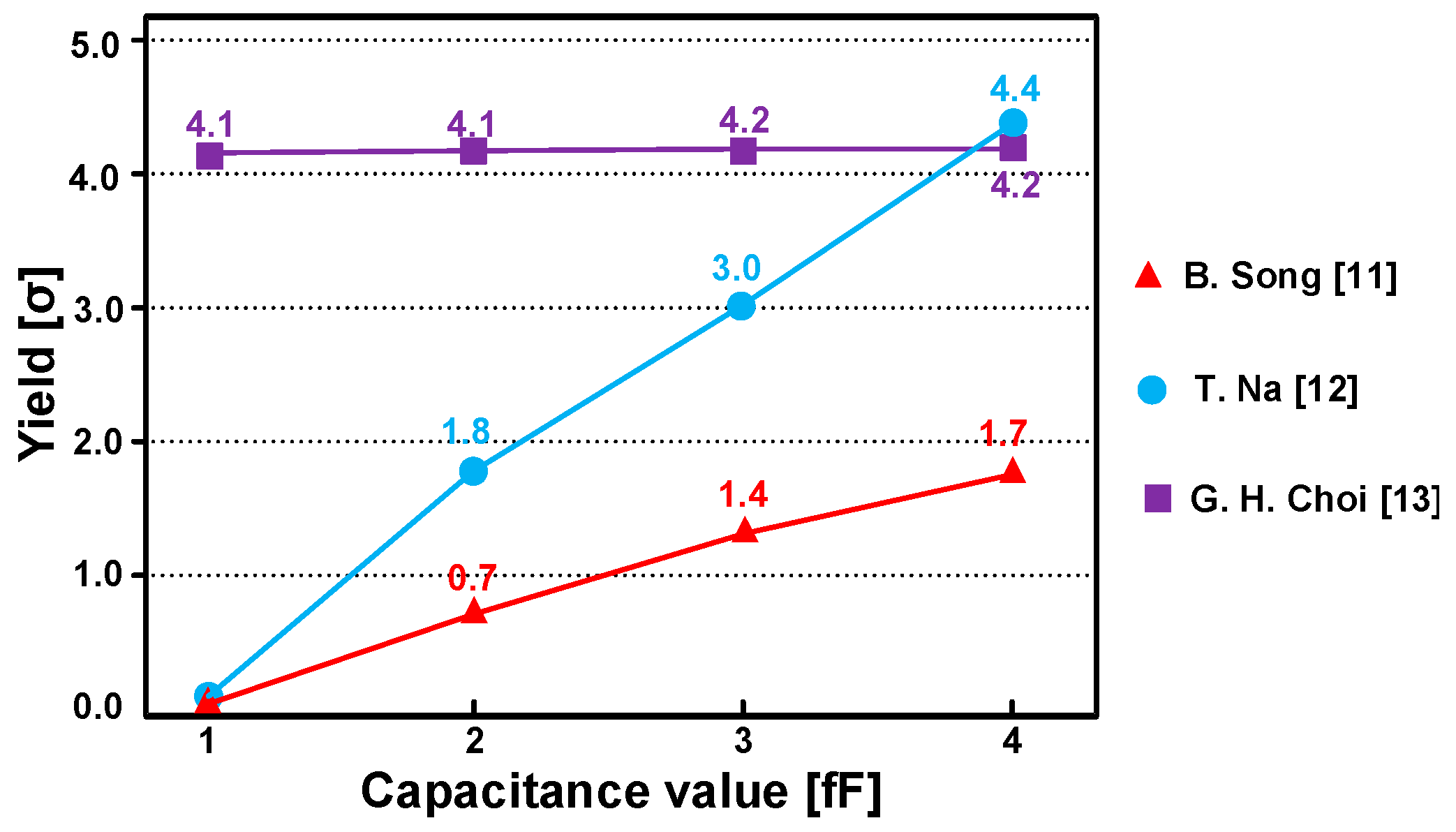

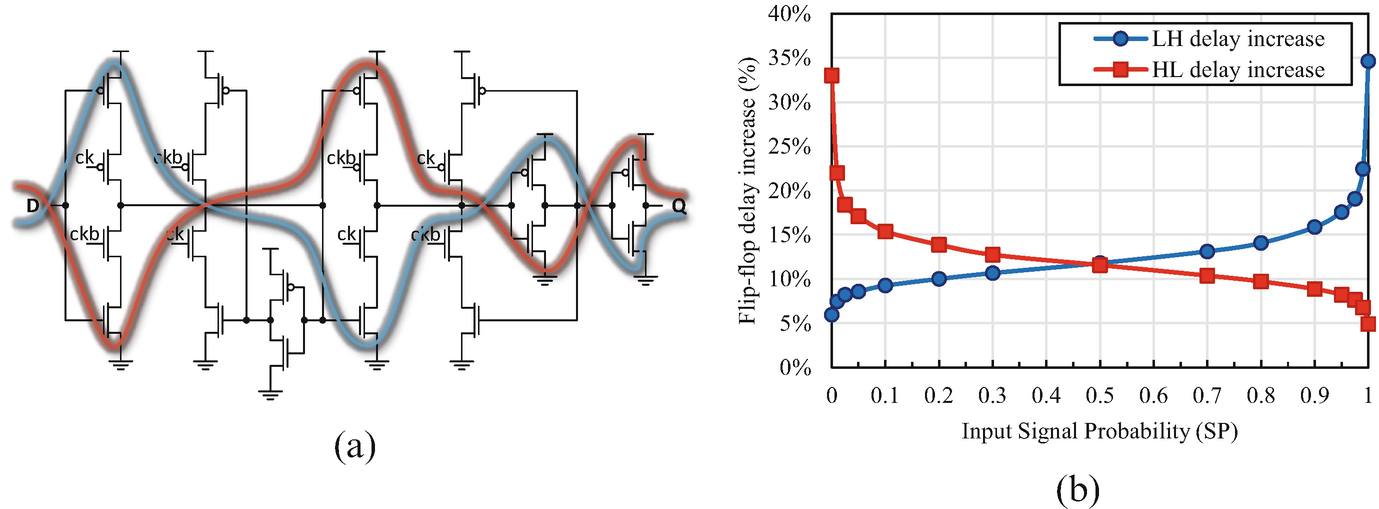

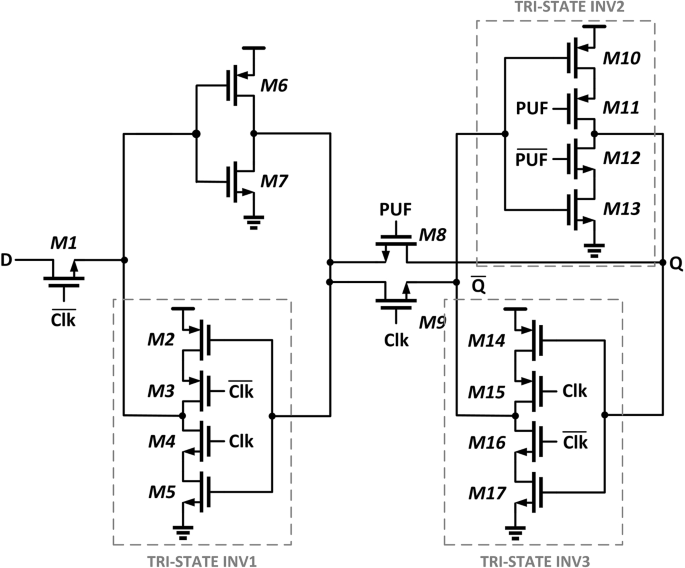

Utilizing manufacturing variations to design a tri-state flip-flop PUF for IoT security applications | SpringerLink

Flip flop comprising two inverters (I and II); static noise voltage... | Download Scientific Diagram

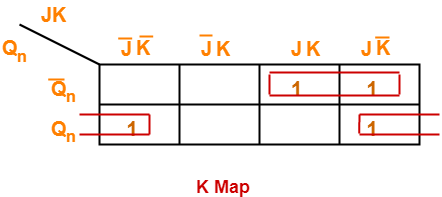

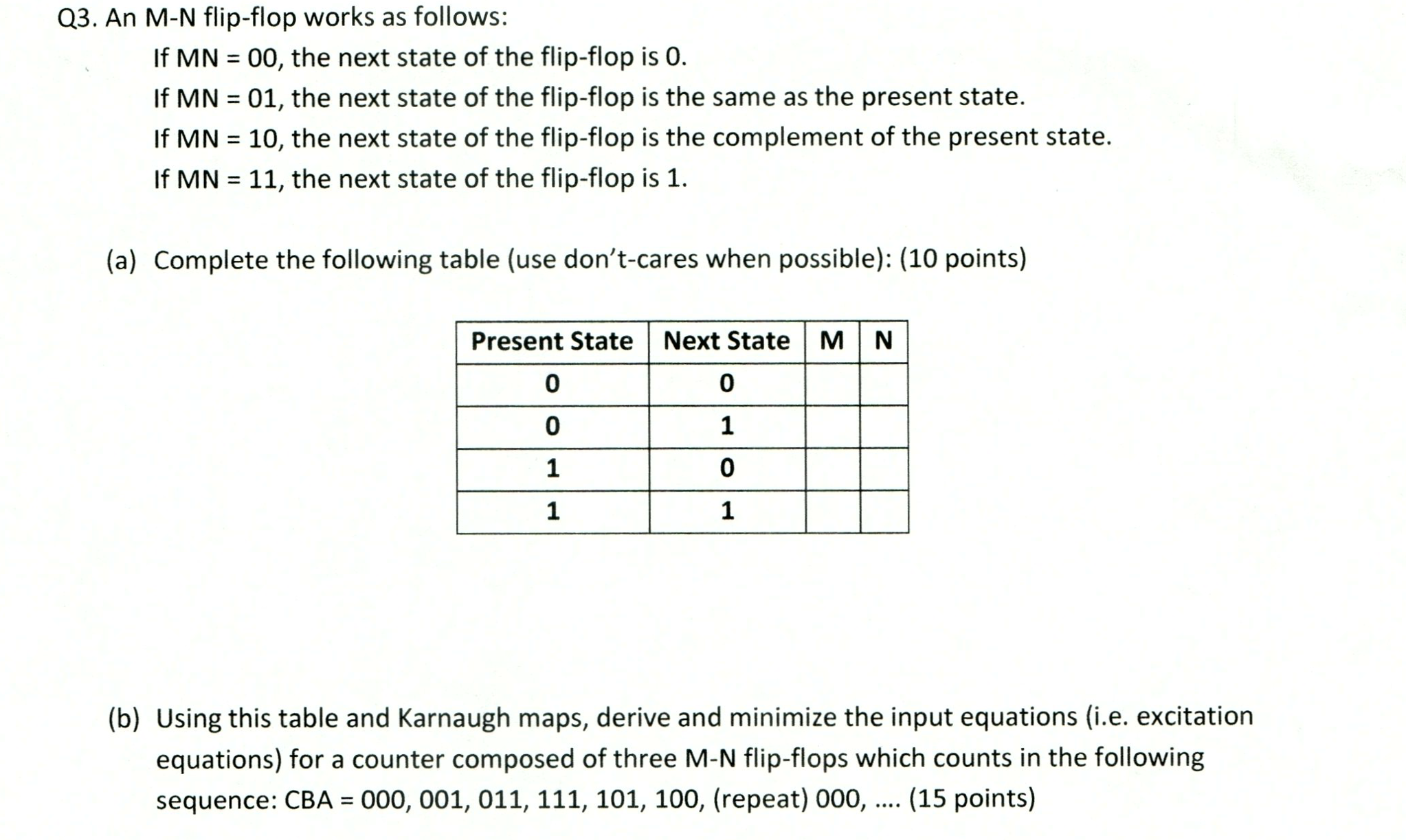

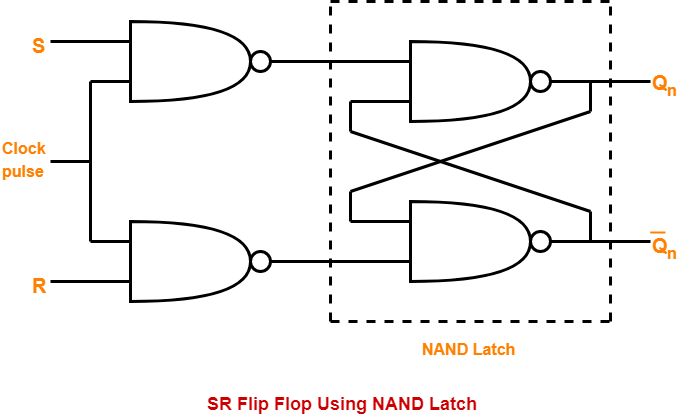

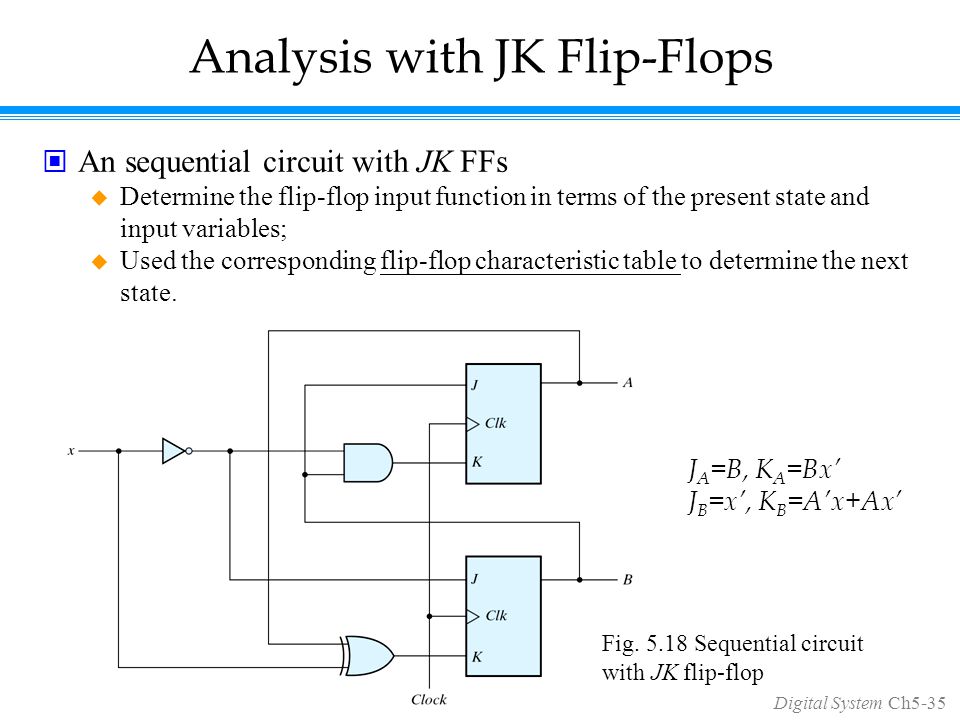

Digital Circuits State Reduction and Assignment State Reduction reductions on the number of flip-flops and the number of gates a reduction in the. - ppt download

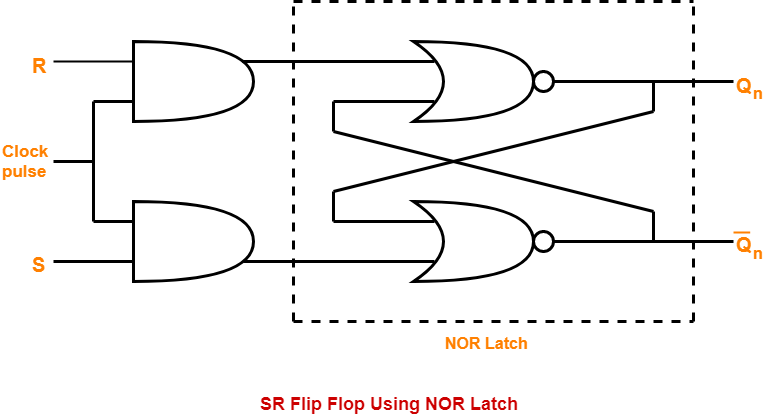

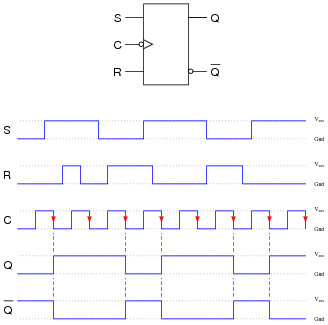

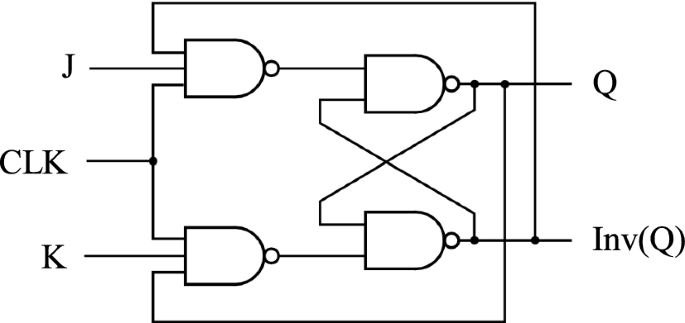

Digital System Ch5-1 Chapter 5 Synchronous Sequential Logic Ping-Liang Lai ( 賴秉樑 ) Digital System 數位系統. - ppt download

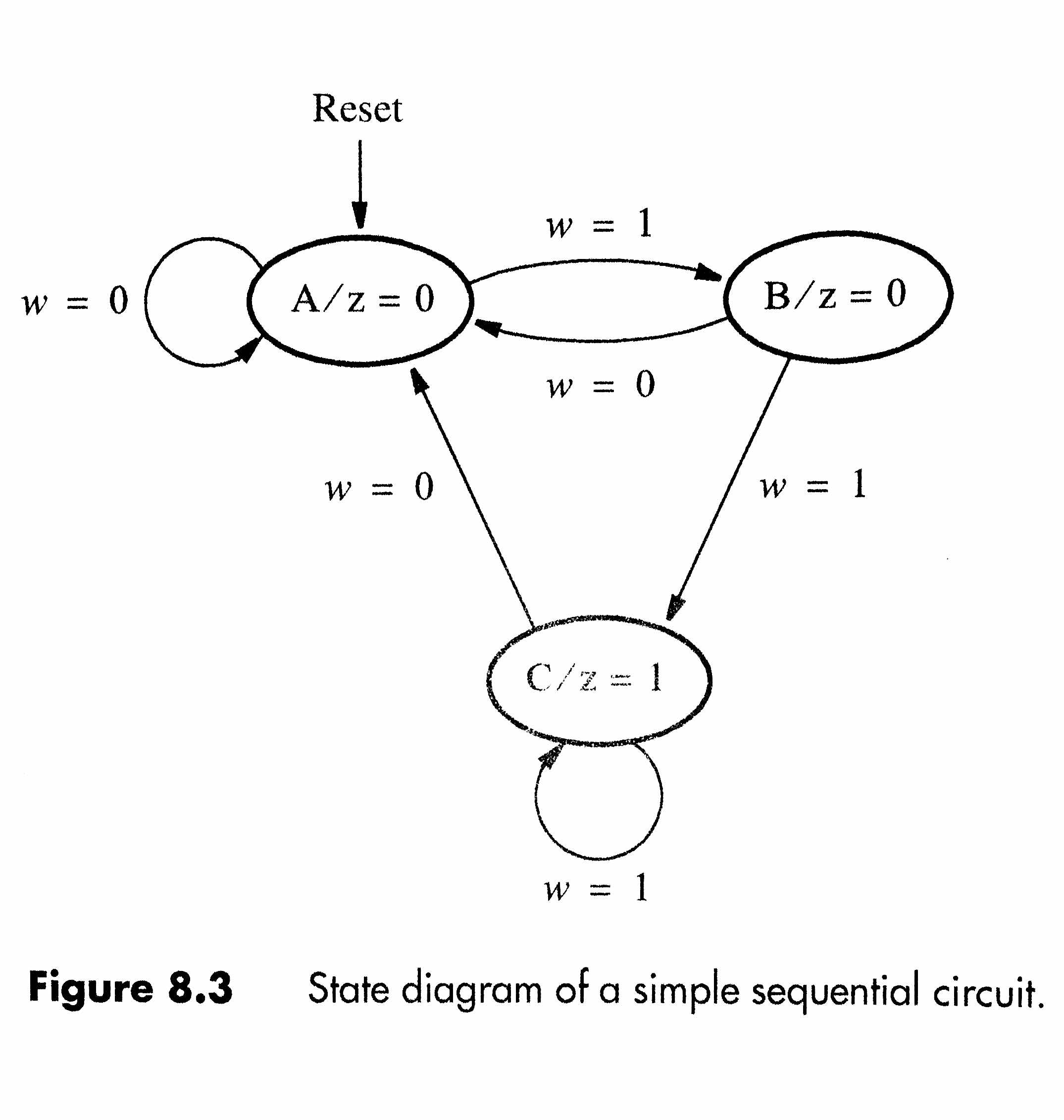

![9.6 One-Hot Encoding Method - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book] 9.6 One-Hot Encoding Method - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]](https://www.oreilly.com/library/view/introduction-to-digital/9780470900550/images/ch009-f026.jpg)

9.6 One-Hot Encoding Method - Introduction to Digital Systems: Modeling, Synthesis, and Simulation Using VHDL [Book]